# Introduction to VHDL Based on Altera's Tutorial

# **Computer Architecture**

# **Prof. Erivelton G. Nepomuceno**

#### nepomuceno@ufsj.edu.br

Copyright © 2003 Altera Corporation

# **Course Outline**

- VHDL Basics

- Design Units

- Architecture Modeling Fundamentals

- Understanding VHDL and Logic Synthesis

- Hierarchical Designing

# **VHDL Basics**

- IEEE industry standard hardware description language

- High-level description language for both Simulation & Synthesis

- 1980 U.S. Department of Defense (DOD) funded a project to create a standard hardware description language under the Very High Speed Integrated Circuit (VHSIC) program.

- 1987 the Institute of Electrical and Electronics Engineers (IEEE) ratified as IEEE Standard 1076.

- 1993 the VHDL language was revised and updated to IEEE 1076 '93.

# Terminology

- HDL Hardware Description Language is a software programming language that is used to model a piece of hardware

- Behavior Modeling A component is described by its input/output response

- Structural Modeling A component is described by interconnecting lower-level components/primitives

# Terminology

- Register Transfer Level (RTL) A type of behavioral modeling, for the purpose of synthesis.

- Hardware is implied or inferred

- Synthesizable

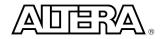

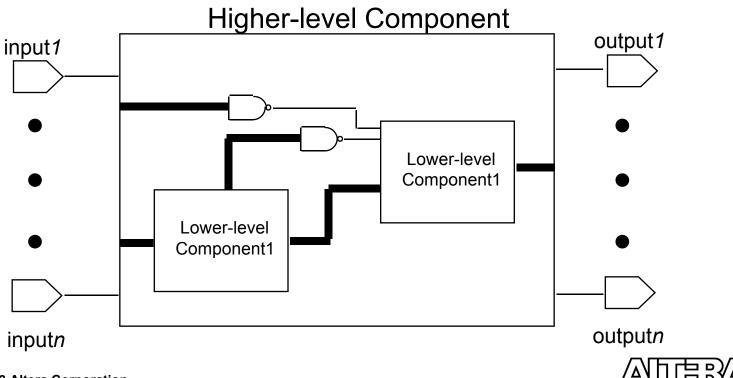

- Synthesis Translating HDL to a circuit and then optimizing the represented circuit

- Process Basic unit of execution in VHDL

# **Behavior Modeling**

Only the functionality of the circuit, no structure

- No specific hardware intent

- For the purpose of synthesis, as well as simulation

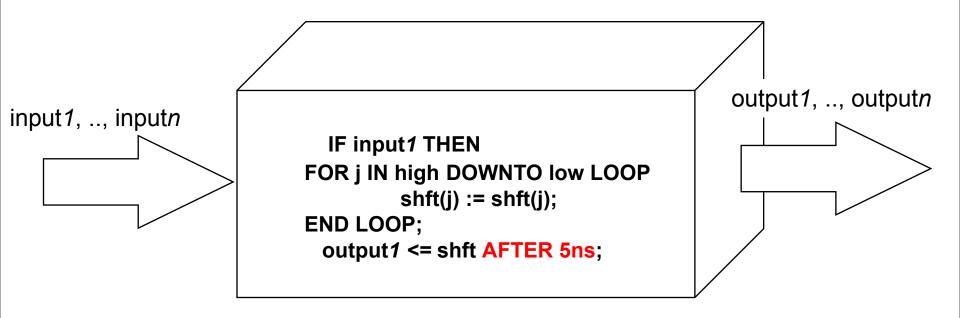

# **Structural Modeling**

- Functionality and structure of the circuit

- Call out the specific hardware

- For the purpose of synthesis

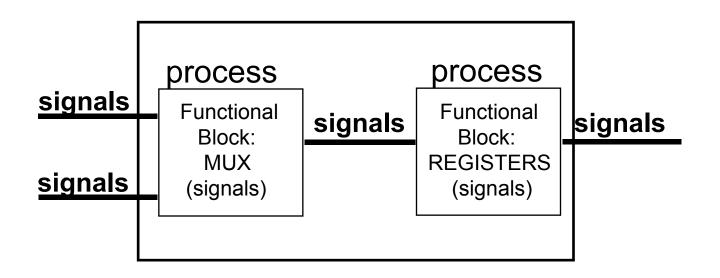

# **RTL Synthesis**

# **VHDL Synthesis vs. Other HDL Standards**

#### VHDL

- "Give me a circuit whose output only changes when there is a low-to-high transition on a particular input.

When the transition happens, make the output equal to the input until the next transition."

- Result: VHDL Synthesis provides a positive edgetriggered flipflop

- ABEL, PALASM, AHDL

- "Give me a D-type flipflop."

- Result: ABEL, PALASM, AHDL synthesis provides a Dtype flipflop. The sense of the clock depends on the synthesis tool.

# **More VHDL Basics**

- Two sets of constructs:

- Synthesis

- Simulation

- The VHDL Language is made up of reserved keywords.

- The language is, for the most part, NOT case sensitive.

- VHDL statements are terminated with a ;

- VHDL is white space insensitive. Used for readability.

- Comments in VHDL begin with "--" to eol

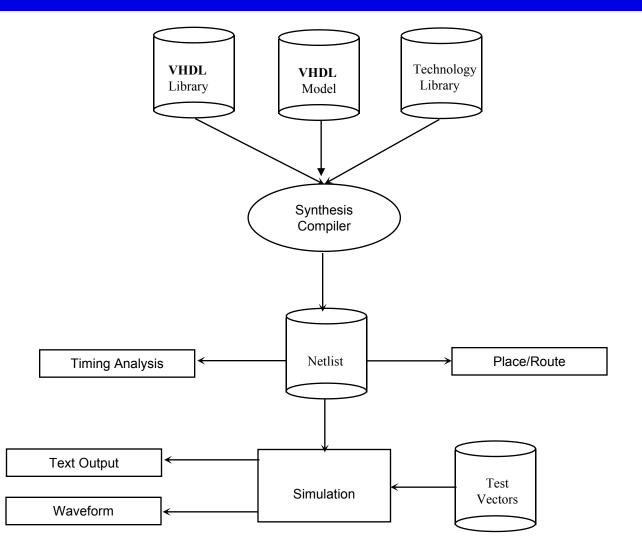

# **Typical Synthesis Design Flow**

Copyright © 2003 Altera Corporation

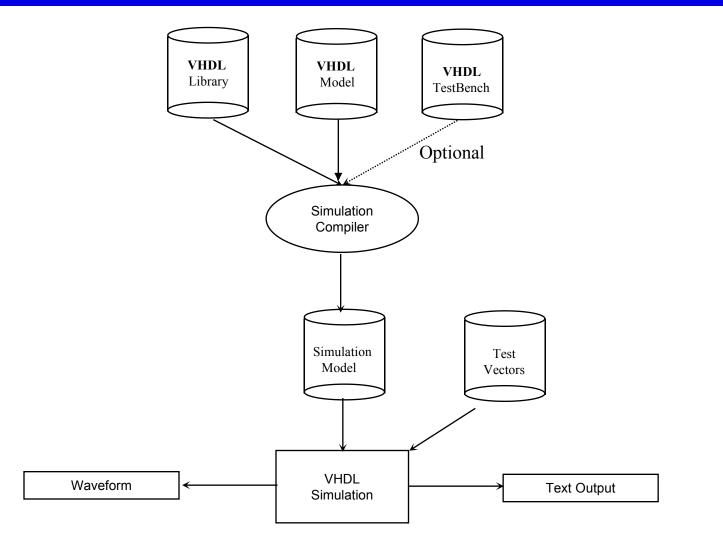

# **Typical Simulation Design Flow**

# VHDL Design Units

Copyright © 2003 Altera Corporation

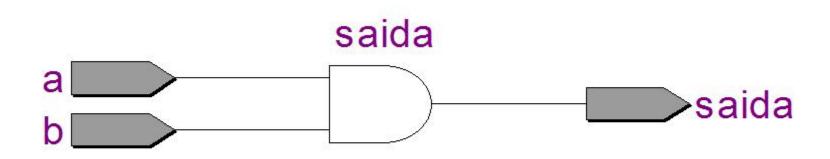

# **Design Units**

#### VHDL Design Units

- Entity

- Used to define external view of a model. i.e. symbol

- Architecture

- Used to define the function of the model. i.e. schematic

- Configuration

- Used to associate an Architecture with an Entity

- Package

- Collection of information that can be referenced by VHDL models. I.e. Library

- Consist of two parts Package Declaration and Package Body.

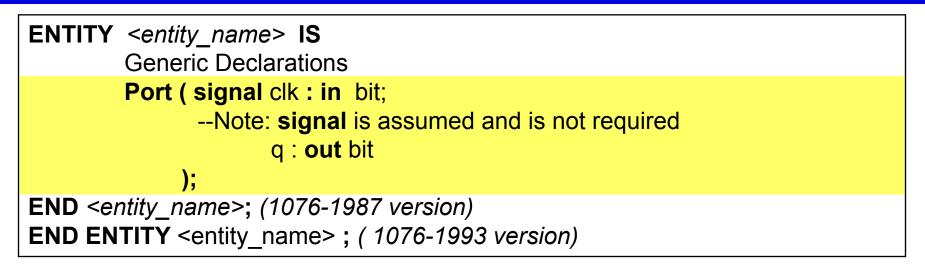

# **Entity Declaration**

ENTITY <entity\_name> IS

Generic Declarations

Port Declarations

END <entity\_name>; (1076-1987 version)

END ENTITY <entity\_name> ; ( 1076-1993 version)

- Analogy : Symbol

- <entity\_name> can be any alpha/numerical name

- Note: MAX+PLUS II requires that the <entity\_name> and <file\_name> be the same

- Generic Declarations

- Used to pass information into a model

- MAX+PLUS II places some restriction on the use of Generics

- Port Declarations

- Used to describe the inputs and outputs i.e. pins

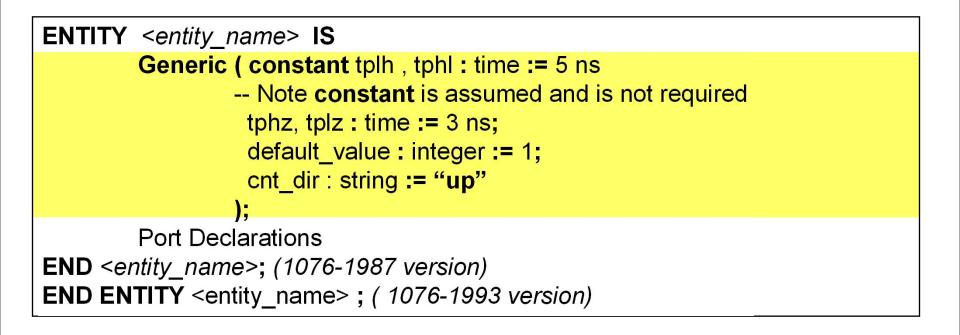

# **Entity : Generic Declaration**

- New values can be passed during compilation

- During simulation/synthesis a Generic is read only

# **Entity : Port Declarations**

Structure : <class> object\_name : <mode> <type> ;

- <class> : what can be done to an object

- Object name : identifier

- <mode> : directional

- » in (input) out (output)

- **inout** (bidirectional) **buffer** (output w/ internal feedback)

- <type> : What can be contained in the object

### Architecture

#### Key aspects of the Architecture

- Analogy : schematic

- Describes the Functionality and Timing of a model

- Must be associated with an ENTITY

- ENTITY can have multiple architectures

- Architecture statements execute concurrently

- Architecture Styles

- Behavioral : How designs operate

- RTL : Designs are described in terms of Registers

- Functional : No timing

- Structural : Netlist

- Gate/Component Level

- Hybrid : Mixture of the above

# Configuration

- Used to make associations within models

- Associate a Entity and Architecture

- Associate a component to an Entity-Architecture

- Widely used in Simulation environments

- Provides a flexible and fast path to design alternatives

- Limited or no support in Synthesis environments

CONFIGURATION <identifier> OF <entity\_name> IS FOR <architecture\_name> END FOR; END; (1076-1987 version) END CONFIGURATION; (1076-1993 version)

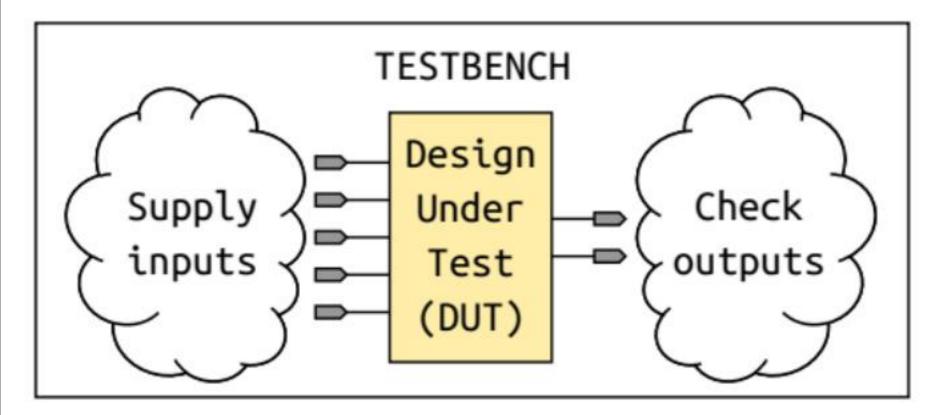

## Testbench

- Testbench is not defined by the VHDL Language Reference Manual and has no formal definition

- In general, it consists of three parts

- 1. The component we want to test, i.e. the *Design Under Test* (DUT).

- 2. A mechanism for supplying inputs to the DUT.

- 3. A mechanism for checking the outputs of the DUT against expected outputs.

#### **Testbench**

Testbench architecture, Source: Kashani-Akhavan. Available at https://goo.gl/dCsMNK

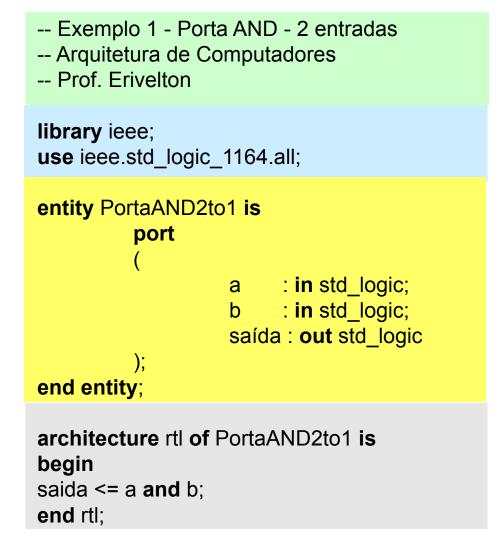

# **Putting It All Together**

#### Compilation using Quartus II

Quartus II 64-Bit - C:/Users/user/Downloads/projeto3/and

| Eile    | <u>E</u> dit <u>V</u> iew <u>P</u> rojec | t <u>A</u> ssignments P <u>r</u> o | cessing <u>T</u> ools |

|---------|------------------------------------------|------------------------------------|-----------------------|

|         | <u>N</u> ew                              | Ctrl+N                             |                       |

| 2       | <u>O</u> pen                             | C41+0                              | ₽₽×                   |

|         | Close                                    | Ctrl+F4                            |                       |

| 1       | New Project <u>W</u> izard               |                                    | /hdl/mod              |

| 1       | Open P <u>r</u> oject                    | Ctrl+J                             |                       |

|         | Save Projec <u>t</u>                     |                                    |                       |

|         | Clos <u>e</u> Project                    |                                    | •                     |

|         | <u>S</u> ave                             | Ctrl+S                             |                       |

|         | Save <u>A</u> s                          |                                    | ₽ ₽ ×                 |

| ø       | Save All                                 | Ctrl+Shift+S                       | omize                 |

|         | Eile Properties                          |                                    |                       |

| oration |                                          |                                    | 100                   |

Copyright © 2003 Altera Corporation

#### Compilation using Quartus II

| Directory, Name, Top-Level Entity [page 1 of 5]                                                                     |                                       |

|---------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| What is the working directory for this project?                                                                     |                                       |

| C:/Users/user/Google Drive/teaching/201801/arqcomp/vhdl/quartus                                                     |                                       |

| Vhat is the name of this project?                                                                                   |                                       |

| PortaAND2to 1                                                                                                       |                                       |

| /hat is the name of the top-level design entity for this project? This name is case sensitive and must exactly matc | h the entity name in the design file. |

| PortaAND2to1                                                                                                        |                                       |

| Jee Existing Project Settings                                                                                       |                                       |

|                                                                                                                     |                                       |

|                                                                                                                     |                                       |

|                                                                                                                     |                                       |

|                                                                                                                     |                                       |

|                                                                                                                     |                                       |

|                                                                                                                     |                                       |

|                                                                                                                     |                                       |

|                                                                                                                     |                                       |

|                                                                                                                     |                                       |

|                                                                                                                     |                                       |

|                                                                                                                     |                                       |

|                                                                                                                     |                                       |

|                                                                                                                     |                                       |

|                                                                                                                     |                                       |

|                                                                                                                     |                                       |

|                                                                                                                     |                                       |

Copyright © 2003 Altera Corporation

| 1 | New Project Wizard                                                                     |

|---|----------------------------------------------------------------------------------------|

|   | Directory, Name, Top-Level Entity [page 1 of 5]                                        |

| 1 | What is the working directory for this project?                                        |

|   | C:/Users/user/Google Drive/teaching/201801/arqcomp/vhdl/quartus                        |

|   | What is the name of this project?                                                      |

|   | PortaAND2to1                                                                           |

|   | What is the name of the top-level design entity for this project? This name is case se |

|   | PortaAND2to1                                                                           |

Use Existing Project Settings...

| New Project Wizard                                                    |            |            |                                      |             | l               |

|-----------------------------------------------------------------------|------------|------------|--------------------------------------|-------------|-----------------|

| Add Files [page 2 of 5]                                               |            |            |                                      |             |                 |

| Select the design files you want to include in the project. Click Add | All to add | all design | files in the project directory to th | e project.  |                 |

| Note: you can always add design files to the project later.           |            |            |                                      |             |                 |

| File name:                                                            |            |            |                                      |             | Add <u>A</u> dd |

| File Name                                                             | Туре       | Library    | Design Entry/Synthesis Tool          | HDL Version | Add Al          |

| /modelsim/Exemplo1_PortaAND2to1/PortaAND2to1.vhd                      | VHD        |            |                                      | Default     |                 |

|                                                                       |            |            |                                      |             | Rem             |

Uр

| Device family                   |                           |       |           | Sh          | now in 'Availal      | ble devices' list                  |          |    |   |  |

|---------------------------------|---------------------------|-------|-----------|-------------|----------------------|------------------------------------|----------|----|---|--|

| Eamily: Cyclor                  | ne IV E                   |       |           | ▼ Pa        | Package: Any         |                                    |          |    | 1 |  |

| Arria I                         | Arria II GX               |       |           |             |                      |                                    | 2        | 5  |   |  |

|                                 | Cyclone II<br>Cyclone III |       |           |             |                      | Any                                |          |    |   |  |

| Target d Cyclor                 | ne III LS                 |       |           | Sp          | p <u>e</u> ed grade: | Any                                |          | 1  |   |  |

| <ul> <li>Auto Cyclor</li> </ul> | ne IV E                   |       |           | Na          | ame filter:          |                                    |          |    |   |  |

| Cyclor                          | ne V (E/GX/GT/SX/SI       | E/ST) |           |             |                      |                                    |          |    |   |  |

| Spec MAX II<br>MAX V            |                           |       |           |             | Show adva            | nced devices HardCopy compatib     | ole only |    |   |  |

| O Othe MAX 30                   | 000A                      |       |           | -           |                      |                                    |          |    |   |  |

| <u>v</u> ailable devices        | :                         |       |           |             |                      |                                    |          |    |   |  |

| Name                            | Core Voltage              | LEs   | User I/Os | Memory Bits | s f                  | Embedded multiplier 9-bit elements | PLL      | G  | * |  |

| EP4CE6E22A7                     | 1.2V                      | 6272  | 92        | 276480      | 30                   |                                    | 2        | 10 |   |  |

| EP4CE6E22C6                     |                           | 6272  | 92        | 276480      | 30                   |                                    | 2        | 10 |   |  |

| EP4CE6E22C7                     |                           | 6272  | 92        | 276480      | 30                   |                                    | 2        | 10 |   |  |

| EP4CE6E22C8                     |                           | 6272  | 92        | 276480      | 30                   |                                    | 2        | 10 |   |  |

| EP4CE6E22C8L                    |                           | 6272  | 92        | 276480      | 30                   |                                    | 2        | 10 |   |  |

| EP4CE6E22C9L                    |                           | 6272  | 92        | 276480      | 30                   |                                    | 2        | 10 | - |  |

| P4CE6E2217                      | 1 7/                      | 6272  | 97        | 276480      | 30                   |                                    | 2        | 10 |   |  |

Copyright © 2003 Altera Corporation

| DA tools:                                                                       |                  |                                                              |                                                           |

|---------------------------------------------------------------------------------|------------------|--------------------------------------------------------------|-----------------------------------------------------------|

| Tool Type                                                                       | Tool Name        | Format(s)                                                    | Run Tool Automatically                                    |

| Design Entry/Synthesis    Vone>   Run this tool automatically to synthesize the |                  | Run this tool automatically to synthesize the current design |                                                           |

| Simulation                                                                      | ModelSim-Altera  | ▼ VHDL                                                       | Run gate-level simulation automatically after compilation |

| Formal Verification                                                             | <none></none>    | *                                                            |                                                           |

| Board-Level                                                                     | Timing           | <none></none>                                                |                                                           |

|                                                                                 | Symbol           | <none></none>                                                | <b>•</b>                                                  |

|                                                                                 | Signal Integrity | <none></none>                                                | •                                                         |

|                                                                                 | Boundary Scan    | <none></none>                                                | *                                                         |

|                                                                                 |                  |                                                              |                                                           |

Copyright © 2003 Altera Corporation

| Summary [page 5 of 5]                                          |                                                                 |

|----------------------------------------------------------------|-----------------------------------------------------------------|

| When you click Finish, the project will be created with the fi | ollowing settings:                                              |

| Project directory:                                             | C:/Users/user/Google Drive/teaching/201801/arqcomp/vhdl/quartus |

| Project name:                                                  | PortaAND2to1                                                    |

| Fop-level design entity:                                       | PortaAND2to1                                                    |

| Number of files added:                                         | 1                                                               |

| Number of user libraries added:                                | 0                                                               |

| Device assignments:                                            |                                                                 |

| Family name:                                                   | Cyclone IV E                                                    |

| Device:                                                        | AUTO                                                            |

| EDA tools:                                                     |                                                                 |

| Design entry/synthesis:                                        | <none> (<none>)</none></none>                                   |

| Simulation:                                                    | ModelSim-Altera (VHDL)                                          |

| Timing analysis:                                               | 0                                                               |

| Operating conditions:                                          |                                                                 |

| Core voltage:                                                  | n/a                                                             |

| Junction temperature range:                                    | n/a                                                             |

|                                                                |                                                                 |

|                                                                |                                                                 |

|                                                                |                                                                 |

| <u>File E</u> dit <u>V</u> iew <u>P</u> rojec | st | <u>A</u> ssignments                                                                               | Processing        | <u>T</u> ools | <u>W</u> indow | <u>H</u> elp | P |  |  |

|-----------------------------------------------|----|---------------------------------------------------------------------------------------------------|-------------------|---------------|----------------|--------------|---|--|--|

| 🗋 😂 🖬 🥔 🐰 🛛                                   |    | 300                                                                                               | PortaAND2t        | 01            |                | 8            |   |  |  |

| roject Navigator                              |    |                                                                                                   | ₽ <i>₽</i> >      | <             |                |              |   |  |  |

| Files                                         |    |                                                                                                   |                   |               |                |              |   |  |  |

| abd/modelsim/Exem-                            |    | <u>Open</u><br><u>Remove File from Project</u>                                                    |                   |               |                |              |   |  |  |

|                                               | 3  | Set as Top-Lev                                                                                    | el <u>E</u> ntity |               | Ct             | rl+Shift+    | 3 |  |  |

| Alierarchy                                    |    | Create <u>A</u> HDL Include Files for Current File<br>Create <u>Symbol Files for Current File</u> |                   |               |                |              |   |  |  |

| ow: Compilation                               |    | Properties                                                                                        |                   |               |                |              |   |  |  |

| <u>File Edit View Project Assignments</u> | Proc          | essing                             | <u>T</u> ools                 | <u>W</u> indow     | <u>H</u> elp | P        |

|-------------------------------------------|---------------|------------------------------------|-------------------------------|--------------------|--------------|----------|

| 9 0 🖉 🖉 🕹 🖓 🖓 🖓                           | •             | <u>S</u> top P                     | rocessin                      | g                  |              | Ctrl+Shi |

| Project Navigator                         |               | Start g                            |                               | Ctrl+L             |              |          |

| Files                                     |               | Analyz<br>St <u>a</u> rt<br>Update |                               |                    |              |          |

| < [                                       | •             |                                    | ation <u>R</u> e<br>nic Synth | port<br>esis Repor | t            | Ctrl+R   |

| Alierarchy 📄 Files 🗗 Design Ui            | <i>∳</i><br>₩ | 12.13                              | Play Pow<br>nalyzer T         | er Analyze         | r Tool       |          |

| ocessing           | Tools                        | 🛛 Window Help 💎                     |                      |                                        |                       |            |         |       |                              |                            |     |                   |       |  |

|--------------------|------------------------------|-------------------------------------|----------------------|----------------------------------------|-----------------------|------------|---------|-------|------------------------------|----------------------------|-----|-------------------|-------|--|

| PortaAND2          |                              | Run Simulation Tool                 | •                    | 24                                     |                       |            | 10      | 0 0   | 1                            | R.                         | 4   | 1                 | 4     |  |

| ₽ <i>₽</i>         | ŝ                            |                                     |                      | Report - PortaAND2to1                  |                       |            |         |       |                              |                            |     | ×                 |       |  |

|                    | Launch Design Space Explorer |                                     | Flow Summary         |                                        |                       |            |         |       |                              |                            |     |                   |       |  |

| aAND2to: 🝈 TimeQue |                              | TimeQuest Timing Analyzer           |                      | 1000                                   | Status<br>rtus II 64- | Bit Versi  | on      |       |                              |                            |     | 1on Ma<br>156 04/ | 0.000 |  |

|                    |                              | Advisors                            | ۲                    | Revision Name<br>Top-level Entity Name |                       |            |         |       | PortaAND2to1<br>PortaAND2to1 |                            |     | 3                 |       |  |

|                    |                              | Chip Planner                        | Family               |                                        |                       |            |         |       | Cyclone IV E                 |                            |     |                   |       |  |

|                    | -                            | Design Partition Planner            | Total logic elements |                                        |                       |            |         |       | 1/6,272 ( < 1 % )            |                            |     |                   |       |  |

|                    |                              | Netlist <u>V</u> iewers             | •                    | 2                                      | RTL Viev              | ver        |         | r     |                              | 16.05                      |     | 1%)               |       |  |

| ₽ <i>₽</i>         | m                            | SignalTap II Logic Analyzer         |                      | -                                      | State Ma              | achine Vi  | ewer    |       |                              |                            |     | ,                 |       |  |

| Customize.         |                              |                                     |                      | Technology Map Viewer (Pos             |                       |            |         |       | st- <u>M</u> apping)         |                            |     |                   |       |  |

|                    |                              |                                     |                      | Technology Map Viewer (Post-Fitting)   |                       |            |         |       |                              | g)                         | )%) |                   |       |  |

|                    | 01                           | In-System Sources and Probes Editor | L                    | Emb                                    | edded Mu              | tiplier 9- | bit ele | ments | 0                            | / 30 (                     | 0%) |                   |       |  |

|                    |                              | SignalProbe Pins                    |                      | Total PLLs<br>Device                   |                       |            |         |       |                              | 0 / 2 (0 %)<br>EP4CE6E22C6 |     |                   |       |  |

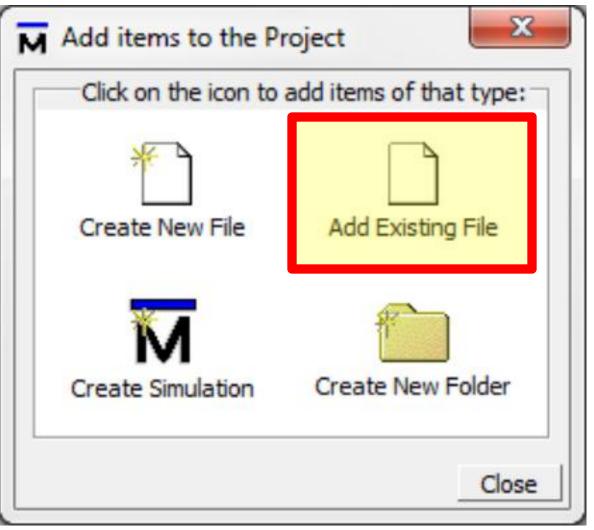

# **Example 1 - Testbench**

- -- Exemplo 1 Porta AND 2 entradas Testbench

- -- Arquitetura de Computadores

- -- Prof. Erivelton

```

library ieee;

use ieee.std_logic_1164.all;

```

```

entity tb_PortaAND2to1 is

end tb_PortaAND2to1;

```

```

architecture behavior of tb_PortaAND2to1 is

-- Declaração de componente de: Unit Uder Test (UUT)

```

```

component PortaAND2to1

port

(

a : in std_logic;

b : in std_logic;

a saída : out std_logic

);

```

#### **Example 1 – Testbench - Continued**

```

-- Sinais

signal a : std_logic;

signal b : std_logic;

signal saida : std logic;

begin

-- Definição the Unit Under Test (UUT)

uut: PortaAND2to1 port map

a => a.

b => b,

saida => saida

);

```

#### **Example 1 – Testbench - Continued**

```

-- Stimulus process

stim proc: process

begin

-- insert stimulus here

wait for 5 ns;

a <= '0':

b <= '0';

wait for 5 ns;

a <= '1':

b <= '0':

wait for 5 ns;

a <= '0';

b <= '1';

wait for 5 ns;

a <= '1':

b <= '1':

wait:

end process;

Copyright © 2003 Alt end architecture:

```

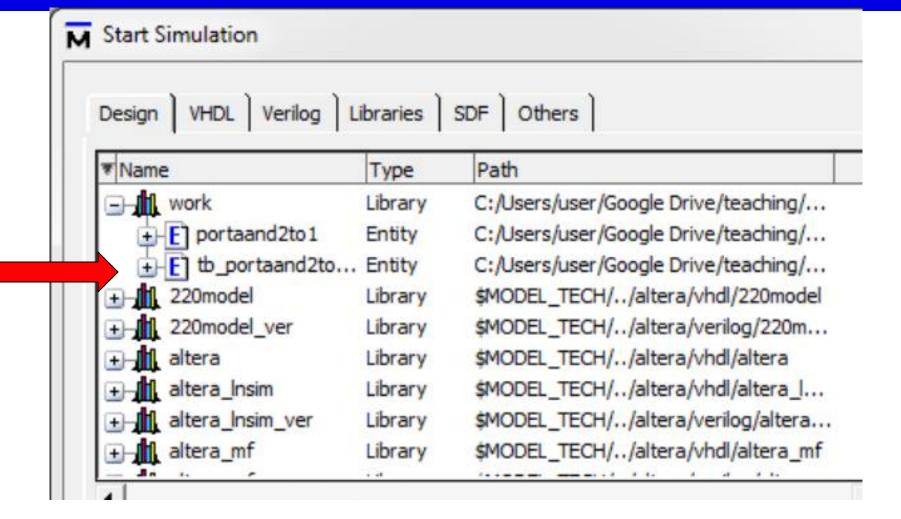

| ile Edit View Compile | Sir | mulate Add Libra | ry Tools Layo               |

|-----------------------|-----|------------------|-----------------------------|

| New                   |     | Eolder           | MEM                         |

| <u>O</u> pen          |     | Source •         |                             |

| Load                  | •   | Project          | <b>  ▼</b>   <i>©</i> } - ( |

| Close                 |     | Library          |                             |

| Import                | •   | Debug Archive    |                             |

| Export                | ۲ ۱ | MODEL TECH/      | /altera/vhdl/220mc          |

| Save Ctrl+S           | ĺ   |                  | /altera/verilog/220         |

| Save As               | Į.  |                  | /altera/vhdl/altera         |

| Report                | ĺ   |                  | /altera/vhdl/altera         |

| Change Directory      | ļ   |                  | /altera/verilog/alte        |

| Use Source            | ļ   |                  | /altera/vhdl/altera         |

| Source Directory      | y   | \$MODEL_TECH/    | /altera/verilog/alte        |

| And2to1                                          |                |

|--------------------------------------------------|----------------|

| Project Location                                 |                |

| C:/Users/user/Google Drive                       | /teachi Browse |

| Default Library Name                             |                |

| work                                             |                |

|                                                  |                |

| Copy Settings From                               | - 20           |

| Copy Settings From<br>0/modelsim_ase/modelsim.in | i Browse       |

| 🌙 🗢 📕 « modelsim                                                                                                                                               | Exemplo1_PortaAND2to1                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| anizar 🔻 🛛 Nova pas                                                                                                                                            | ta                                              |

| <ul> <li>Favoritos</li> <li>Área de Trabalho</li> <li>Downloads</li> <li>intelecto</li> <li>2017sbai-coletivc</li> <li>Google Drive</li> <li>Locais</li> </ul> | Nome<br>work<br>PortaAND2to1<br>tb_PortaAND2to1 |

| File Edit View    | Compile Simulate A          | dd Project Tools Layout                 |  |

|-------------------|-----------------------------|-----------------------------------------|--|

| 🖹 • 🚘 🗑 🤹         | , 🍜   🤾 🖻 🏙 😂 🕻             | 2   💿 - 🎮 🖭 🖬 📙 🆃 🗄                     |  |

| ColumnLayout A    | llColumns                   | ↓ / · · · · · · · · · · · · · · · · · · |  |

| Froject - C:/User | s/user/Google Drive/teachin | g/201801/argcomp/simulation/And2t       |  |

| ▼ Name            | Status Type Ord             | e Modified                              |  |

| PortaAND2tr       |                             | 05/06/18 02:08:06 PM                    |  |

| tb_PortaA         | Edit<br>Execute             | 05/06/18 02:15:14 PM                    |  |

|                   | Compile                     | Compile Selected                        |  |

|                   | Add to Project              | Compile All                             |  |

|                   | Remove from Project         | Compile Out-of-Date                     |  |

| Close Project     |                             | Compile Order                           |  |

|                   | Update                      | Compile Report                          |  |

| 2                 |                             | Compile Summary                         |  |

|                   | Properties                  |                                         |  |

| File Edit View Com            | pile Simulate Add                                                | P    | roject                 | Tools                              | Layout   | Boo     |

|-------------------------------|------------------------------------------------------------------|------|------------------------|------------------------------------|----------|---------|

| ] 🖻 • 🚘 🖬 🤹 🎆                 | 🤞 🖻 🎆 🎦 🚞                                                        |      | ) · 🖗                  | 8: <b>M</b>                        | i 🛛 🕸    | 🔠 🥉     |

| ColumnLayout AllColu          | umns                                                             |      |                        | -     «                            | 8 · 4    | - 🤣     |

| 🔠 Project - C:/Users/user/    | Google Drive/teaching/20                                         | ) 18 | 01/arqcor              | mp/simul                           | ation/An | d2to1 : |

| ▼ Name                        | Status Type Order M                                              | odit | fied                   |                                    |          |         |

| PortaAND2to1.vh <sup>-1</sup> | Edit<br>Execute                                                  |      | 5/18 02:0<br>5/18 02:1 | 5:14 PM                            |          |         |

|                               | Compile                                                          |      | Comp                   | ile Selec                          | ted      |         |

|                               | Add to Project<br>Remove from Project<br>Close Project<br>Update | •    | Comp                   | ile Out-o<br>ile Ordei<br>ile Repo | r<br>rt  |         |

|                               | Properties<br>Project Settings                                   | -    |                        | ile Sumn<br>ile Prope              |          | -       |

| Optimizatio<br>mulation<br>e <u>O</u> ptions | 0    |                        | ] #          | ·        |

|----------------------------------------------|------|------------------------|--------------|----------|

|                                              |      |                        | )) »<br>(- 4 | <u> </u> |

| e <u>O</u> ptions                            |      |                        | š - 🐴        | - 6      |

|                                              |      | 100                    |              |          |

|                                              |      | <ul> <li>Ma</li> </ul> | ation/And    | d2to     |

|                                              |      |                        |              |          |

| ini.                                         |      | М                      |              |          |

|                                              |      | M                      |              |          |

|                                              | Brea | ak 🛛                   |              |          |

|                                              | t    |                        | Break        | Break    |

| • | <u>File Edit Viev</u>                        | w <u>C</u> ompile <u>S</u> i | imulate A    | A <u>d</u> d St |

|---|----------------------------------------------|------------------------------|--------------|-----------------|

|   | 🖹 • 🚘 🔒                                      | 🤹 🎆   🐰 🖣                    | <b>) 🕼 🏠</b> | <u>````   (</u> |

| L | ColumnLayout                                 | AllColumns                   |              |                 |

|   | 🔊 sim - Default 🗉                            |                              |              | ₫ X             |

| A | Instance                                     | Desig                        | n unit 🛛 De  | sign ur         |

| 4 | □     tb_porta==<br>↓-     uut<br>↓-     uut | View Declaration             | n            | cti.            |

| Ŀ | sta dare                                     | Add Wave                     | Ctrl+W       | e               |

|   | std_logi                                     | Add Wave New<br>Add Wave To  |              | e<br>, e        |

|   |                                              | Add Dataflow<br>Add to       | Ctrl+D       |                 |

|   |                                              | Conv                         | CHLLC        | _               |

Copyright

|   | Wave - Default        |           |    |

|---|-----------------------|-----------|----|

|   | ▲                     | Msgs      |    |

|   | /tb_portaand2to1/a    | U         |    |

|   | /tb_portaand2to1/b    | U         |    |

|   | /tb_portaand2to1/s    | . U       |    |

|   |                       |           |    |

|   |                       |           |    |

|   |                       |           |    |

|   |                       |           |    |

|   |                       |           |    |

|   |                       |           |    |

|   |                       |           |    |

|   |                       |           |    |

|   | z                     |           |    |

|   |                       |           |    |

|   |                       |           |    |

|   |                       |           |    |

|   |                       |           |    |

|   |                       |           |    |

| × | Now                   | 0 ps      | 11 |

|   | Toggle leaf names <-> |           | 7  |

|   | loggie lear names <-> | rui names | 21 |

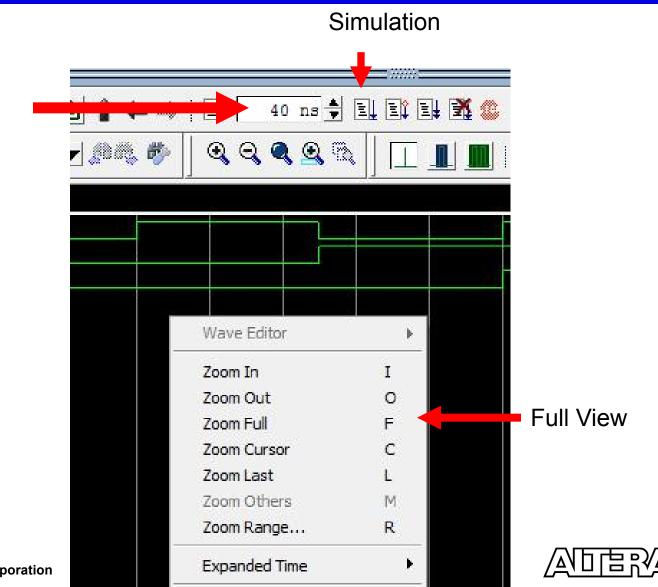

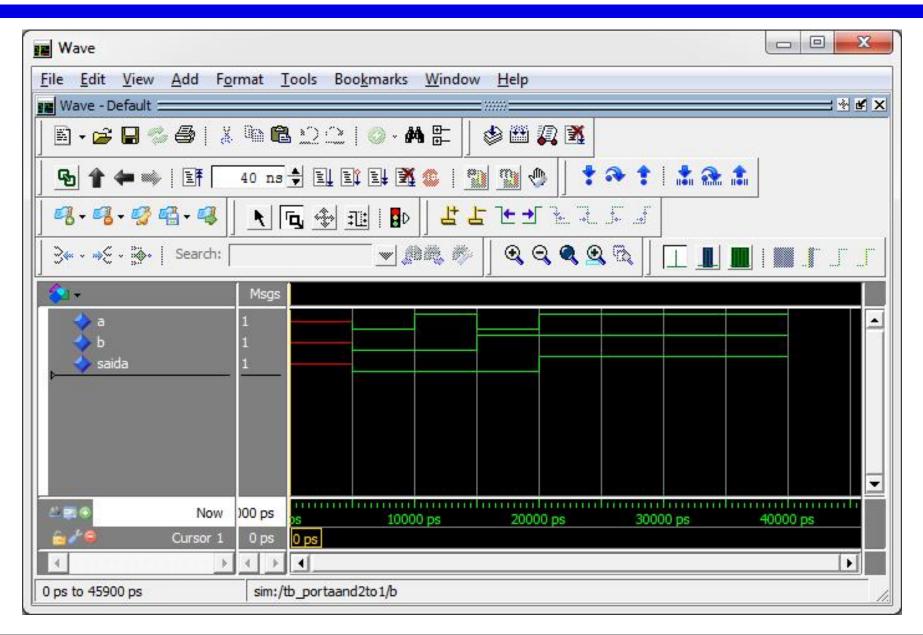

**Simulation Time**

🔐 C:\Users\user\Google Drive\teaching\201801\arqcomp\vhdl\modelsim\Exemplo1\_PortaAND2to1\tb\_my\_project.do - Notepad++ [A File Edit Search View Encoding Language Settings Tools Macro Run Plugins Window ? ) 🕘 🗄 🐚 💫 | 🔏 🐚 🎁 | 🤉 😋 | 🏙 🍢 | 🤏 👒 | 💁 🔂 🗐 🖾 🖉 🖾 🖉 💷 💌 💌 💌 🔍 😑 PortaAND2to1.vhd 🔀 🔚 tb\_PortaAND2to1.vhd 🔀 🔚 tb\_my\_project.do 🔀 1 ## NOTE: Do not edit this file. 2 ## 3 pif {[file exists work]} { vdel -lib work -all 4 5 11 6 vlib work vcom -explicit -93 "PortaAND2to1.vhd" 7 vcom -explicit -93 "tb PortaAND2to1.vhd" 8 vsim -t 1ps -lib work tb PortaAND2to1 9 10 #add wave sim:/tb PortaAND2to1/\* 11 do {wave.do} 12 view wave 13 view structure 14 view signals 15 run 0.03us 16 #quit -force

Copyright

| 🔚 Porta AND | 2to1.vhd 🔀 🔚 tb_PortaAND2to1.vhd 🔀 🔚 tb_my_project.do 🔀 🔚 wave.do 🔀 |

|-------------|---------------------------------------------------------------------|

| 1           | onerror {resume}                                                    |

| 2           | quietly WaveActivateNextPane {} 0                                   |

| 3           | add wave -noupdate /tb_portaand2to1/a                               |

| 4           | add wave -noupdate /tb_portaand2to1/b                               |

| 5           | add wave -noupdate /tb_portaand2to1/saida                           |

| 6           | TreeUpdate [SetDefaultTree]                                         |

| 7           | WaveRestoreCursors {{Cursor 1} {0 ps} 0}                            |

| 8           | quietly wave cursor active 1                                        |

| 9           | configure wave -namecolwidth 81                                     |

| 10          | configure wave -valuecolwidth 45                                    |

| 11          | configure wave -justifyvalue left                                   |

| 12          | configure wave -signalnamewidth 1                                   |

| 13          | configure wave -snapdistance 10                                     |

| 14          | configure wave -datasetprefix 0                                     |

| 15          | configure wave -rowmargin 4                                         |

| 16          | configure wave -childrowmargin 2                                    |

| 17          | configure wave -gridoffset 0                                        |

| 18          | configure wave -gridperiod 1                                        |

| 19          | configure wave -griddelta 40                                        |

| 20          | configure wave -timeline 0                                          |

| 21          | configure wave -timelineunits ns                                    |

| 22          | update                                                              |

| 23          | WaveRestoreZoom {0 ps} {31500 ps}                                   |

| Fi | le Edit Vi      | ew 🤇    | Compile | Sim | ulate Ac             | bb       |

|----|-----------------|---------|---------|-----|----------------------|----------|

|    | New             |         |         |     | 🕵 🔊 d                | ×        |

|    | <u>O</u> pen    |         |         |     | ·····                | ····     |

|    | <u>L</u> oad    |         |         |     |                      |          |

|    | <u>C</u> lose   |         |         | H   |                      | 202      |

| Á  | I <u>m</u> port |         |         | •   | } <mark>≪</mark> ~ ? | <u>ي</u> |

|    | <u>Export</u>   |         |         | ۰E  |                      |          |

| 4  | Save Transc     | ript    | Ctrl+S  | F   | Della                |          |

|    | Save Transc     | ript As |         | H   | Path                 |          |

|    | Report          |         |         |     | C:/Use               | 100      |

|    | Change Dire     | ctory   | 0       |     | \$MODE<br>\$MODE     | 877      |

|    | Use Source.     | <i></i> |         |     | SMODE                | 877      |

| 4  | Source Direc    | tory    |         |     | \$MODE               | 1        |

|    | Datasets        |         |         |     | \$MODE               | 157      |

|    | Environment     | 6       |         |     | \$MODE               | 100      |

|                       | tory, then select OK.               |

|-----------------------|-------------------------------------|

| C:\Users\user\Google  |                                     |

| Drivaltaschinal 20190 | 1)-secomelubdlimedoloimiExomele 1 D |

| Exemplo1_PortaAND     |                                     |

|                       | a 🍌 modelsim 🔺                      |

|                       | a 📕 Exemple                         |

|                       | ⊳ 퉲 worl                            |

|                       | Exemple                             |

|                       | Exemple                             |

|                       | Exemple                             |

|                       | Exemple                             |

| < []                  |                                     |

| CONTRACT STREET       |                                     |

Copyright © 2003 Altera

| tb_my_project.do              |               |

|-------------------------------|---------------|

|                               |               |

|                               |               |

| 4                             |               |

| ModelSim> do tb_my_project.do |               |

|                               | 0 ps to 36 ps |

| ModelSim ALTERA STARTER EDITION 10.1d                                                      |                                                                                                                 |          |

|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------|

|                                                                                            | izanscript T <u>o</u> ols Layo <u>u</u> t Boo <u>k</u> marks <u>W</u> indow <u>H</u> elp                        | 1        |

| <b>■•☞■◎◎●</b>  ≵ <b>№@</b> ♪⊇ ©                                                           |                                                                                                                 | 1        |

| ColumnLayout Default                                                                       | ▋ 4.44444444444444444444444444444444444                                                                         |          |

| ेरेक - ⇒ि - ड्रेके   Search:                                                               |                                                                                                                 |          |

|                                                                                            | 🏠 Objects                                                                                                       |          |

|                                                                                            | Value Kind Mode 🗛 Msgs                                                                                          |          |

|                                                                                            | a 1 Signal Interna<br>b 1 Signal Interna<br>saida 1 Signal Interna<br>Processes (Active)<br>Type (filtered) Str |          |

|                                                                                            | Casto Now 30 ns ns 5 ns 10 ns 15 ns 20 ns 25 ns<br>€ ≠ € ursor 1 0.00 ns 0.00 ns                                | - 1      |

| 👖 Library 🛛 💾 Call Stack 🗶 🛺 sim 🗶 🔍                                                       |                                                                                                                 | <b>I</b> |

| Transcript                                                                                 |                                                                                                                 |          |

| <pre># .main_pane.structure.interior.cs.body # .main_pane.objects.interior.cs.body.t</pre> |                                                                                                                 | -        |

| /SIM 11> sim:/tb_portaand2to1                                                              |                                                                                                                 | -        |

|                                                                                            | Now: 30 ns Delta: 0 sim:/tb_portaand2to1                                                                        |          |

#### Packages

- Packages are a convenient way of storing and using information throughout an entire model

- Packages consist of:

- Package Declaration (Required)

- Type declarations

- Subprograms declarations

- Package Body (Optional)

- Subprogram definitions

- VHDL has two built-in Packages

- Standard

- TEXTIO

#### Package Example

| LIBRARY ieee;                                               |  |  |

|-------------------------------------------------------------|--|--|

| USE ieee.std_logic_1164.all;                                |  |  |

| PACKAGE filt_cmp IS                                         |  |  |

| <b>TYPE</b> state_type IS (idle, tap1, tap2, tap3, tap4);   |  |  |

| COMPONENT acc                                               |  |  |

| <pre>port(xh : in std_logic_vector(10 downto 0);</pre>      |  |  |

| clk, first: in std_logic;                                   |  |  |

| <pre>yn : out std_logic_vector(11 downto 4));</pre>         |  |  |

| END COMPONENT;                                              |  |  |

| FUNCTION compare (variable a , b : integer) RETURN boolean; |  |  |

| END filt_cmp;                                               |  |  |

| PACKAGE BODY filt_cmp IS                                    |  |  |

| FUNCTION compare (variable a , b : integer) IS              |  |  |

| VARIABLE temp : boolean;                                    |  |  |

| Begin                                                       |  |  |

| If a < b then                                               |  |  |

| temp := true ;                                              |  |  |

| else                                                        |  |  |

| temp := false ;                                             |  |  |

| end if;                                                     |  |  |

| RETURN temp ;                                               |  |  |

| END compare ;                                               |  |  |

| END fily_cmp ;                                              |  |  |

#### Copyright © 2003 Altera Corporation

#### **Package Declaration**

#### **Package Body**

#### Libraries

- Contains a package or a collection of packages

- Resource Libraries

- Standard Package

- IEEE developed packages

- Altera Component packages

- Any library of design units that are referenced in a design

- Working Library

- Library into which the unit is being compiled

### Model Referencing of Library/Package

- All packages must be compiled

- Implicit Libraries

- Work

- STD

- Note: Items in these packages do not need to be referenced, they are implied

- LIBRARY Clause

- Defines the library name that can be referenced

- Is a symbolic name to path/directory

- Defined by the Compiler Tool

#### USE Clause

Specifies the package and object in the library that you have specified in the Library clause

#### Example

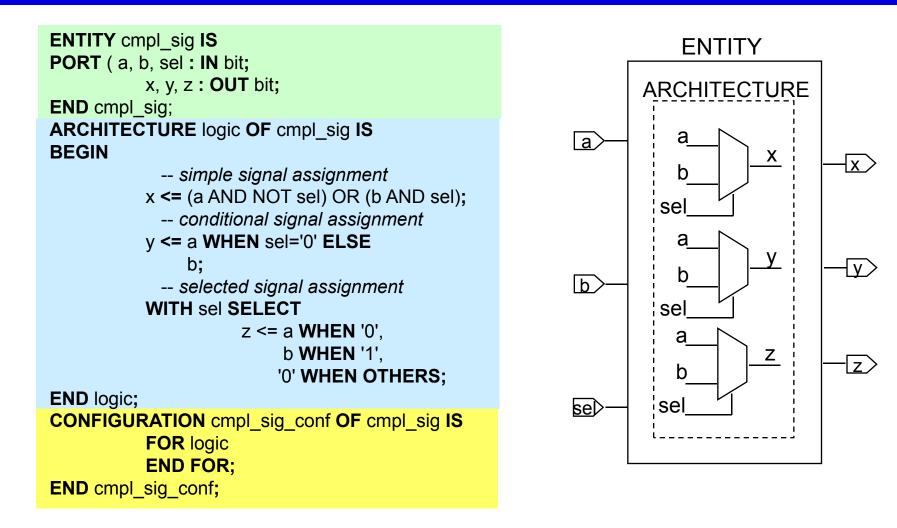

LIBRARY ieee; USE ieee.std logic 1164.all; ENTITY cmpl sig IS **PORT** (a, b, sel : IN std logic; x, y, z : **OUT** std logic; **END** cmpl sig; **ARCHITECTURE** logic **OF** cmpl sig **IS** BEGIN -- simple signal assignment x <= (a AND NOT sel) OR (b AND sel); -- conditional signal assignment y <= a WHEN sel='0' ELSE b; -- selected signal assignment WITH sel SELECT z <= a WHEN '0', b WHEN '1'. '0' WHEN OTHERS; **END** logic; **CONFIGURATION** cmpl sig conf OF cmpl sig IS **FOR** logic END FOR: **END** cmpl sig conf;

LIBRARY <name>, <name> ;

- name is symbolic and define by compiler tool

- Note: Remember that WORK and STD do not need to be defined.

- USE lib\_name.pack\_name.object;

- ALL is a reserved word

- Placing the Library/Use clause 1st will allow all following design units to access it

#### Libraries

#### LIBRARY STD ;

- Contains the following packages:

- **standard** (Types: Bit, Boolean, Integer, Real, and Time. All operator functions to support types)

- **textio** (File operations)

- An implicit library (built-in)

- Does not need to be referenced in VHDL design

### **Types Defined in Standard Package**

- Type BIT

- 2 logic value system ('0', '1')

signal a temp : bit;

- BIT\_VECTOR array of bits

signal temp : bit\_vector(3 downto 0);

signal temp : bit\_vector(0 to 3) ;

- Type BOOLEAN

- (false, true)

- Integer

- Positive and negative values in decimal signal int\_tmp : integer; -- 32 bit number signal int\_tmp1 : integer range 0 to 255; --8 bit number

- Note: Standard package has other types

#### Libraries

#### LIBRARY IEEE;

- Contains the following packages:

- std\_logic\_1164 (std\_logic types & related functions)

- **std\_logic\_arith** (arithmetic functions)

- **std\_logic\_signed** (signed arithmetic functions)

- **std\_logic\_unsigned** (unsigned arithmetic functions)

## Types Defined in std\_logic\_1164 Package

#### Type **STD\_LOGIC**

- 9 logic value system ('U', 'X', '0', '1', 'Z', 'W', 'L', 'H', '-')

- 'W', 'L', 'H" weak values (Not supported by Synthesis)

- 'X' used for unknown

- 'Z' (not 'z') used for tri-state

- '-' Don't Care

- Resolved type: supports signals with multiple drives

#### Type STD\_ULOGIC

- Same 9 value system as STD\_LOGIC

- Unresolved type: Does not support multiple signal drives; Error will occur

### **VHDL Operators**

| <b>Operator Type</b> | Operator Name/Symbol        |

|----------------------|-----------------------------|

| Logical              | and or nand nor xor xnor(1) |

| Relational           | = /= < <= > >=              |

| Adding               | + - &                       |

| Signing              | + -                         |

| Multiplying          | * / mod rem                 |

| Miscellaneous        | ** abs not                  |

Copyright © 2003 Altera Corporation

』 (1) Supported in VHDL '93 only 🖉 🛅 🖳 。

#### **Operator Overloading**

- How do you use Arithmetic & Boolean functions with other data types?

- Operator Overloading defining Arithmetic & Boolean functions with other data types

- Operators are overloaded by defining a function whose name is the same as the operator itself

- Because the operator and function name are the same, the function name must be enclosed within double quotes to distinguish it from the actual VHDL operator

- The function is normally declared in a package so that it is globally visible for any design

#### Review

#### Terminology

- Synthesis

- Behavior Modeling

- Structural Modeling

- Design Units

- Entity

- Architecture

- Configuration

- Package

- Libraries

- work

- ieee

# Architecture Modeling Fundamentals

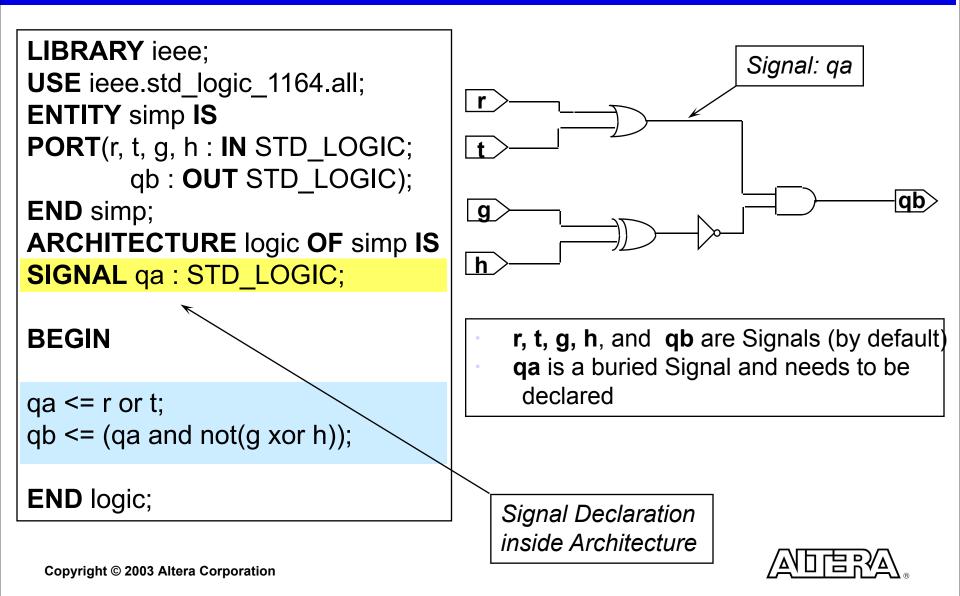

## **Using Signals**

- Signals represent physical interconnect (wire) that communicate between processes (functions)

- Signals can be declared in **Packages**, **Entity** and **Architecture**

### **Assigning Values to Signals**

SIGNAL temp : STD\_LOGIC\_VECTOR (7 downto 0);

All bits:

temp <= "10101010"; temp <= x"AA" ; (1076-1993)

Single bit:

Bit-slicing:

temp (7 downto 4) <= "1010";

Single-bit: single-quote (')

Multi-bit: double-quote (")

### Signal Used As an Interconnect

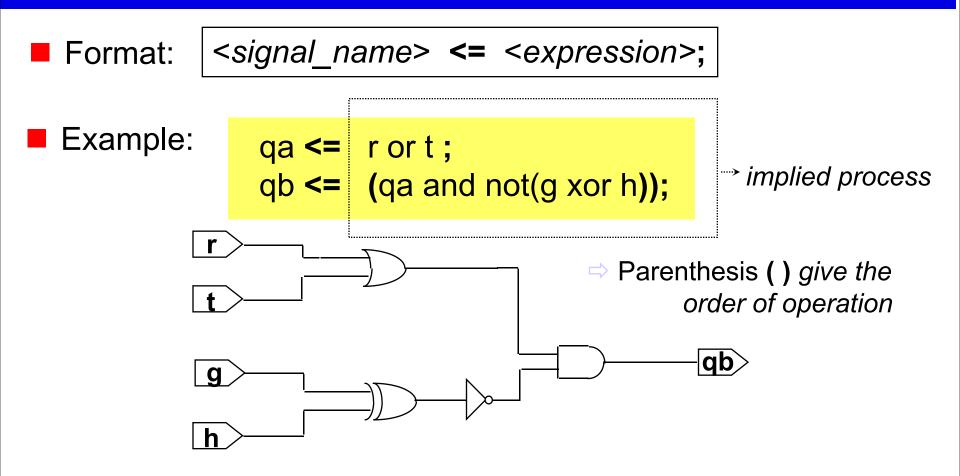

### **Simple Signal Assignments**

VHDL Operators are used to describe the process

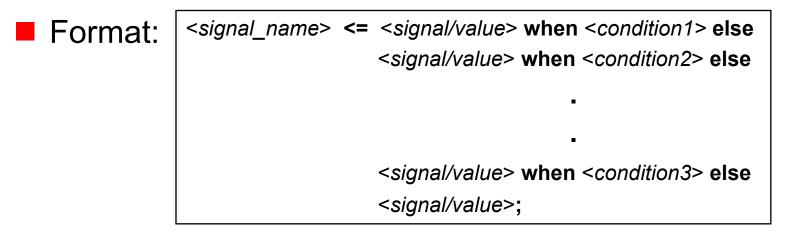

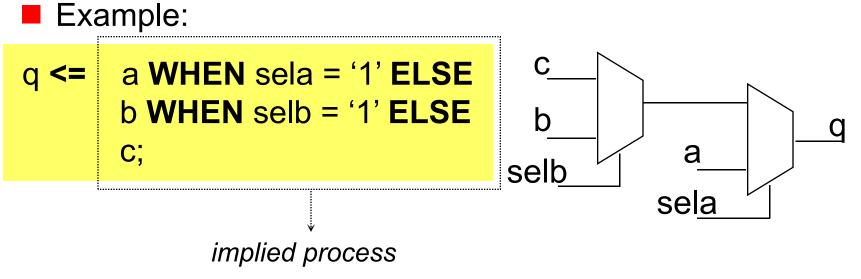

### **Conditional Signal Assignments**

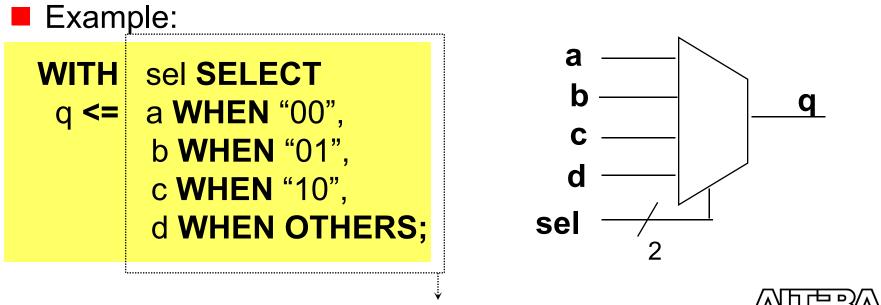

#### **Selected Signal Assignments**

Format:

implied process

#### **If-Then Statements**

#### Format:

IF <condition1> THEN {sequence of statement(s)} ELSIF <condition2> THEN {sequence of statement(s)} . ELSE

{sequence of statement(s)}

END IF;

#### Example:

#### **Case Statement**

#### Format:

Example:

q

sel

```

PROCESS(sel, a, b, c, d)

BEGIN

CASE sel IS

WHEN "00" =>

q <= a:

WHEN "01" =>

q <= b;

WHEN "10" =>

q <= c;

WHEN OTHERS =>

q <= d;

END CASE:

END PROCESS;

```

Copyright © 2003 Altera Corporation

# **Sequential LOOPS**

- Infinite Loop

- Loops infinitely unless EXIT statement exists

- While Loop

- Conditional test to end loop

FOR Loop

Iteration Loop

[loop\_label]LOOP

--sequential statement

EXIT loop\_label;

END LOOP;

WHILE <condition> LOOP

--sequential statements

END LOOP;

FOR <identifier> IN <range> LOOP

--sequential statements

END LOOP;

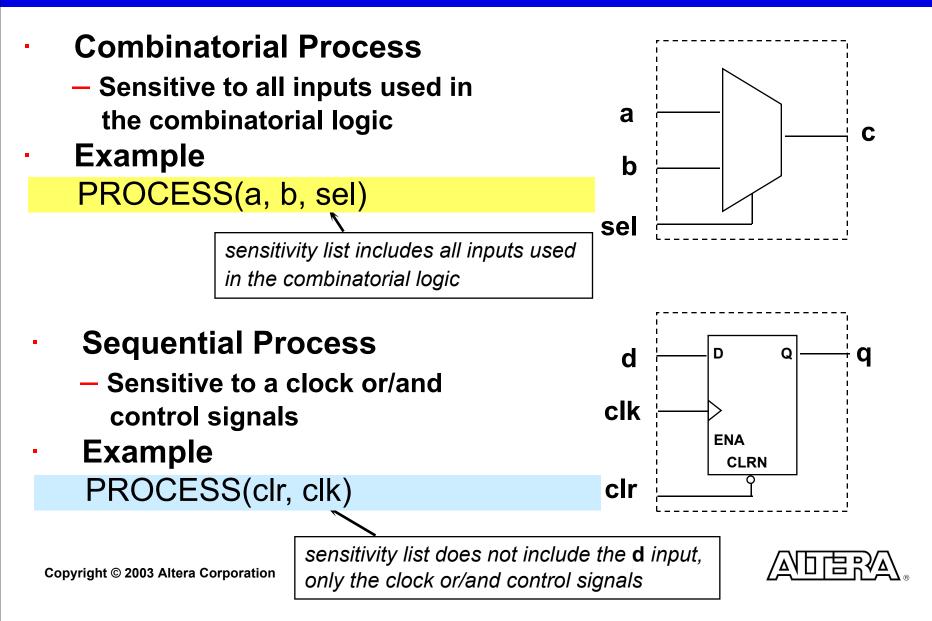

## **Two Types of Process Statements**

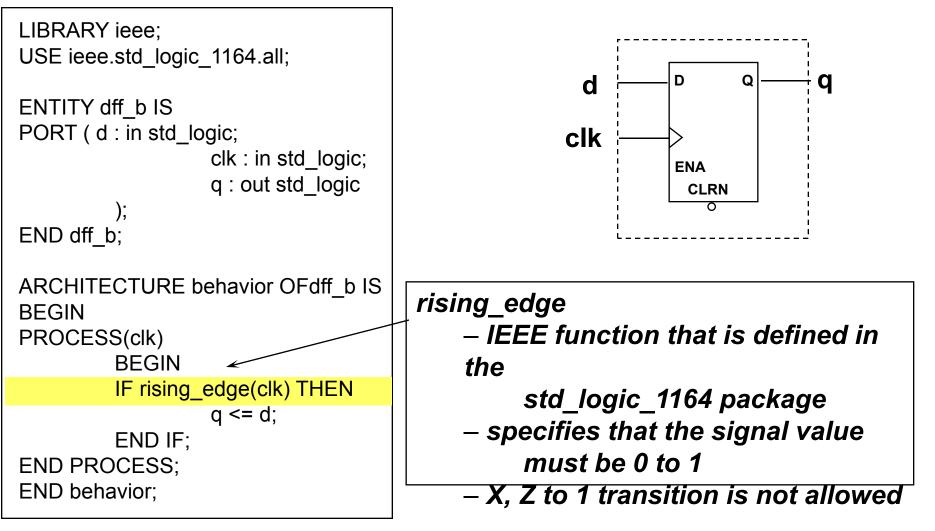

# DFF - rising\_edge

Copyright © 2003 Altera Corporation

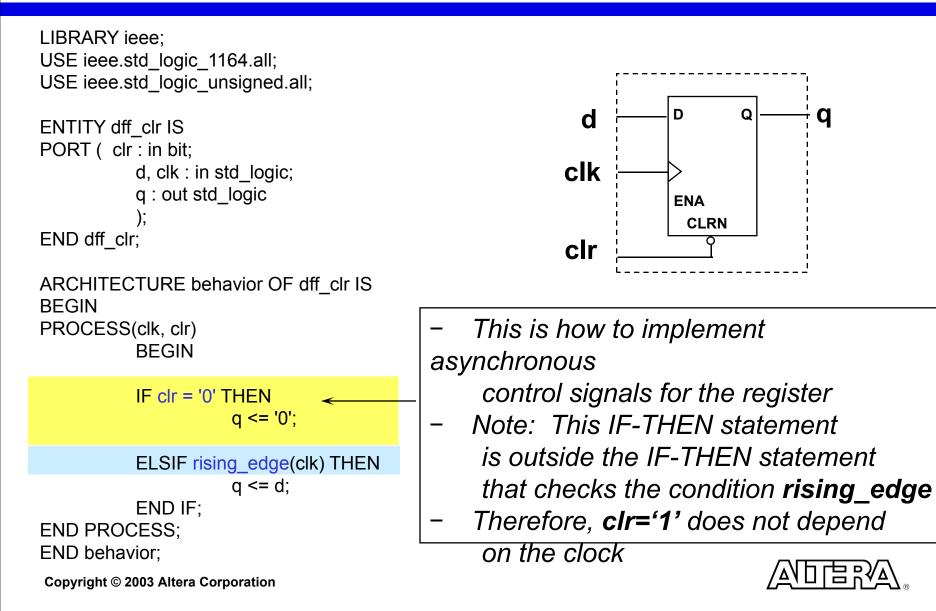

## **DFF** with asynchronous clear

Q

q

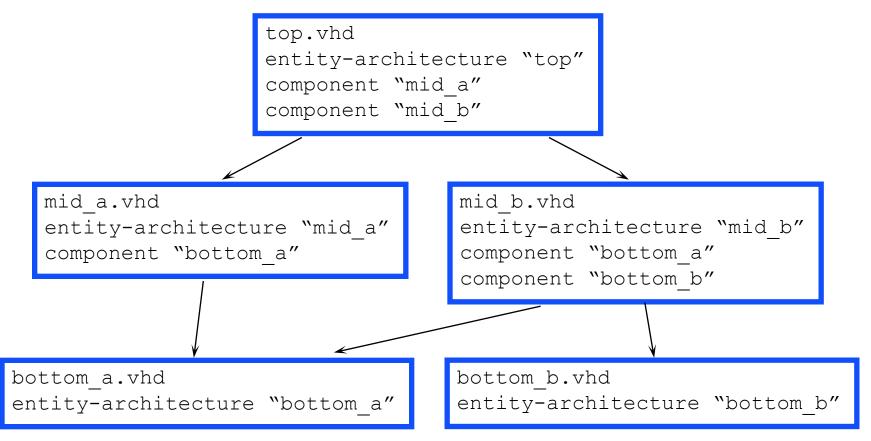

#### **Design Hierarchically - Multiple Design Files**

VHDL hierarchical design requires Component Declarations and Component Instantiations

#### **Component Declaration and Instantiation**

Component Declaration - Used to declare the *Port types* and the *Data Types* of the ports for a lower-level design

**COMPONENT** <lower-level\_design\_name> **IS PORT** ( <port\_name> : <port\_type> <data\_type>;

<port\_name> : <port\_type> <data\_type>);

#### END COMPONENT;

Component Instantiation - Used to map the ports of a lowerlevel design to that of the current-level design

<instance\_name> : <lower-level\_design\_name>

**PORT MAP**(<lower-level\_port\_name> => <current\_level\_port\_name>, ...,<lower-level\_port\_name> => <current\_level\_port\_name>);

#### Library Altera/LPM

#### LIBRARY ALTERA;

- Contains the following packages:

- maxplus2 (Component declarations for all primitives and oldstyle megafunction Altera libraries)

- megacore (Component declarations for some Altera Megacores)

#### LIBRARY LPM;

- Contains the following packages:

- Ipm\_components (Component Declarations for all Altera LPM functions)

- Note: See MAX+PLUS II or Quartus online help for more information

#### **LPM Instantiation**

- All of the Altera LPM macrofunctions are declared in the package Ipm\_components.all in the LIBRARY Ipm;

- The MegaWizard Plug-in Manager in MAX+plus II and Quartus creates the VHDL code instantiating the LPM or Megafunction

- In the VHDL Code:

LIBRARY lpm; USE lpm.lpm\_components.all;

# LPM Instantiation - Ipm\_mult

LIBRARY ieee; USE ieee.std\_logic\_1164.all; USE ieee.std\_logic\_unsigned.all;

LIBRARY lpm; USE lpm.lpm\_components.all;

ARCHITECTURE behavior OF tst\_mult IS

#### BEGIN

u1 : lpm\_mult **GENERIC MAP** (lpm\_widtha => 8, lpm\_widthb => 8, lpm\_widths => 16, lpm\_widthp => 16) **PORT MAP**(dataa => a, datab => b, result => q\_out);

**END** behavior;

Copyright © 2003 Altera Corporation

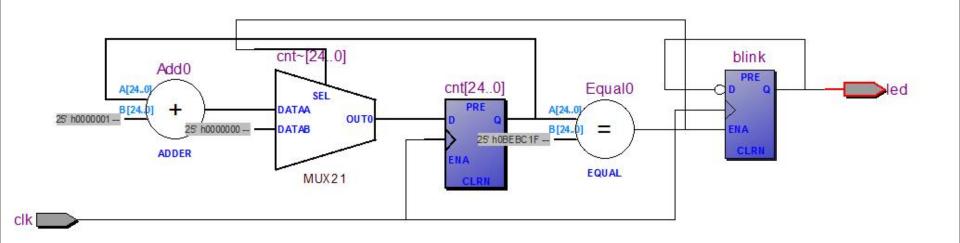

#### **Exemplo 10 - HelloWorld**

Fazer um led piscar a uma frequência de 1 sUtiliza a frequência de 50 MHz

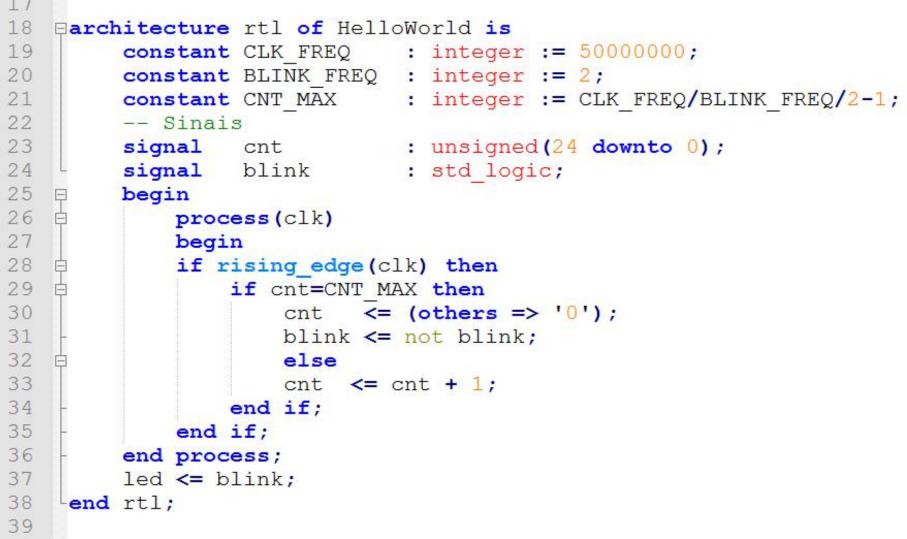

# Exemplo 10 – HelloWorld - VHDL

```

which 🔝 🔚 to_PortaANUZto Evhic 🖾 🔚 Hello World.vhic 🔛

-- Exemplo 10 - HelloWorld

1

2

-- Arquitetura de Computadores

3

-- Prof. Erivelton

4

-- Adaptaed from: Martin Schoeberl

5

6

library ieee;

7

use ieee.std logic 1164.all;

8

use ieee.numeric std.all;

9

10

entity HelloWorld is

11

12

port (

13

clk: in std logic;

14

led: out std logic

15

);

Lend HelloWorld;

16

```

#### Exemplo 10 – HelloWorld – VHDL

Copyright © 2003 Altera Corporation

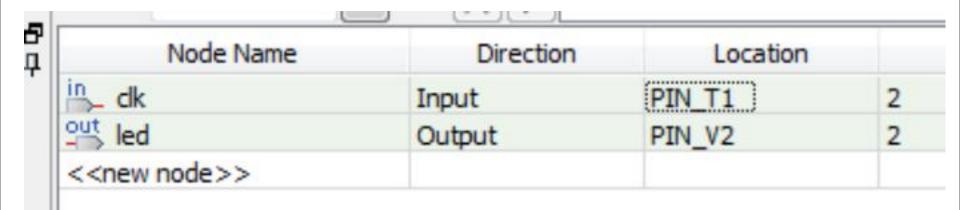

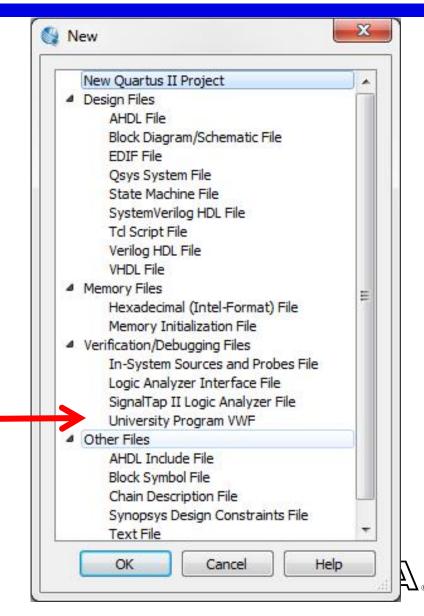

#### **Exemplo 10 – HelloWorld**

- Elaboração de um TestBench para o HelloWord usando o Quartus II -University Program WVF

- Simulação máxima 100 us

- O VHDL precisa ser alterado para comportar esse tempo

- Sugere-se uma frequência de 500 kHz

| <u>F</u> ile | Edit         | <u>View</u> Simulation <u>H</u> elp |         |                                                      |                                                       |

|--------------|--------------|-------------------------------------|---------|------------------------------------------------------|-------------------------------------------------------|

|              | ×            | Delete Del                          |         |                                                      | 副账                                                    |

| Mast         |              | Insert 🔸                            | Inser   | rt Node or Bus                                       | 20.31 ns                                              |

|              |              | Value 🕨                             | -       |                                                      |                                                       |

|              |              | Grouping                            | 80.0 ns | 160.0 ns                                             | 240.0                                                 |

|              |              | Reverse Group or Bus Bit Order      |         |                                                      |                                                       |

|              |              | Radix •                             |         |                                                      | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

|              |              | Grid Size                           |         |                                                      |                                                       |

|              |              | Set End Time                        |         |                                                      |                                                       |

|              | $\checkmark$ | Snap to Grid                        |         |                                                      |                                                       |

|              |              | Snap to Transition                  |         |                                                      |                                                       |

|              | P            | Properties                          |         | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |                                                       |

| lame:        |         | ОК          |

|--------------|---------|-------------|

| ype:         | INPUT   | Cancel      |

| /alue type:  | 9-Level | •           |

| Radix:       | Binary  | Node Finder |

| Bus width:   | 1       |             |

| Start index: | 0       |             |

| Node Finder         |        |               |                |      |  |

|---------------------|--------|---------------|----------------|------|--|

| Named: *            |        | Filter: Pins: | : all          | • Ок |  |

| .ook in: *          |        |               |                | List |  |

| Nodes Found:        |        | Se            | elected Nodes: |      |  |

| Name                | Туре   |               | Name           | Туре |  |

| <mark>i≞_</mark> dk | Input  |               |                |      |  |

| ed led              | Output |               |                |      |  |

|                     |        |               |                |      |  |

|                     |        | >>            |                |      |  |

|                     |        |               |                |      |  |

|                     |        | <<            |                |      |  |

|                     |        |               |                |      |  |

|                     |        |               |                |      |  |

|                     |        |               |                |      |  |

|                     |        |               |                |      |  |

|                     |        | 26 28         |                |      |  |

| Edit | <u>View</u> Simulation Help    |            |                     |            |          |

|------|--------------------------------|------------|---------------------|------------|----------|

| ×    | Delete Del                     | 5)         | 2 XB 👯 👯 🐴 🖪        | 副影         |          |

|      | Insert                         | ·          | Pointer:            | 7.06 ps    |          |

|      | Value                          | · 👗        | Forcing Unknown (X) | Ctrl+Alt+X |          |

|      | Grouping                       | • <u>•</u> | Forcing Low (0)     | Ctrl+Alt+0 | 320.0 ns |

|      | Reverse Group or Bus Bit Order | Å          | Forcing High (1)    | Ctrl+Alt+1 |          |

|      | Radix                          | z          | High Impedance (Z)  | Ctrl+Alt+Z |          |

|      | Grid Size                      | χī         | Weak Low (L)        | Ctrl+Alt+L | *****    |

|      | Set End Time                   | ХH         | Weak High (H)       | Ctrl+Alt+H | ~~~~~    |

| 1    | Snap to Grid                   |            | Invert              | Ctrl+Alt+I |          |

| -    | Snap to Transition             | χc         | Count <u>V</u> alue | Ctrl+Alt+V |          |

|      |                                | Xð         | Overwrite Clock     | Ctrl+Alt+K |          |

|      | Properties                     | X2         | Arbitrary Value     | Ctrl+Alt+B |          |

|      |                                | ХВ         | Random Values       | Ctrl+Alt+R |          |

| ile                | <u>E</u> dit <u>V</u> iew | Simu | lation <u>H</u> e         | lp 🐬                          |             |

|--------------------|---------------------------|------|---------------------------|-------------------------------|-------------|

|                    | ع 🔊 🕲                     |      | Options                   | 20 📾 🛙                        |             |

| Master Time Bar: 0 |                           | R.   | Run Functional Simulation |                               | Pointer: 3. |

|                    |                           | N.   | Run Timin                 |                               |             |

|                    | Name                      | Zin  | Generate                  | ModelSim Testbench and Script | 20.         |

|                    | Name L                    |      | U ps                      | o ha                          |             |

| in_                | dk                        | BO   |                           |                               |             |

| out                | led                       | вх   |                           |                               | ******      |

| Simi   | ulation \                | Waveform E                    | ditor - [HelloWord  | I.sim.vwf (Kead-O                     | nly)j          |                   |          |

|--------|--------------------------|-------------------------------|---------------------|---------------------------------------|----------------|-------------------|----------|

| ile E  | <u>E</u> dit <u>V</u> ie | ew <u>S</u> imulat            | tion <u>H</u> elp 💎 |                                       |                | Search altera.com |          |

|        | <b>ڪ</b> ا               | < <sup>0</sup> <sup>1</sup> ₁ | z XI XH INV X       | <u>c</u> X& X? X <u>R</u>             | t ti 🕯 🔳       |                   |          |

| laster | Time Bar                 | : 0 ps                        | Poin                | ter: 4.36 us Int                      | erval: 4.36 us | Start: End:       |          |

|        | N factor                 | 0 ps                          | 20.48 us            | 40.96 us                              | 61.44 us       | 81.92 us          |          |

|        | Nam                      | 0 ps<br>占                     |                     |                                       |                |                   |          |

| 5-     | <mark>cl</mark> k        |                               |                     |                                       |                |                   |          |

|        | led                      | NNN                           | mmmm                | www.                                  | mmmm           | www.www           | MM       |

|        |                          |                               |                     |                                       |                |                   |          |

|        |                          |                               |                     |                                       |                |                   |          |

| (      | )                        |                               | 1111111             | i i i i i i i i i i i i i i i i i i i |                |                   |          |

|        |                          | g Low                         |                     |                                       |                | 0%                | 00:00:00 |